# EGC442 Class Notes 4/14/2023

#### Baback Izadi

Division of Engineering Programs bai@engr.newpaltz.edu

#### Test 2:

- Chapter 4

- ALU design

- Chapter 5

- Design of data path and control

- Pipelined processor

- Correcting for various hazards

- Advanced pipeline concepts

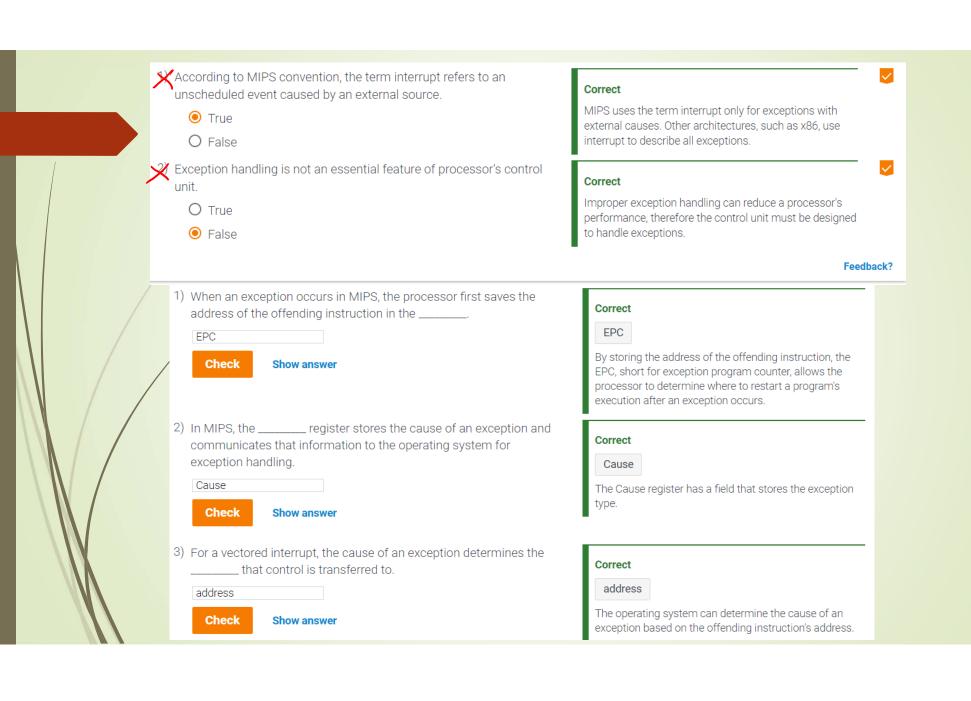

#### Exception

- Exception: Also called interrupt. An unscheduled event that disrupts program execution; used to detect overflow.

- Interrupt: An exception that comes from outside of the processor. (Some architectures use the term interrupt for all exceptions.)

- Vectored interrupt: An interrupt for which the address to which control is transferred is determined by the cause of the exception

| Type of event                                 | From where? | MIPS terminology       |

|-----------------------------------------------|-------------|------------------------|

| I/O device request                            | External    | Interrupt              |

| Invoke the operating system from user program | Internal    | Exception              |

| Arithmetic overflow                           | Internal    | Exception              |

| Using an undefined instruction                | Internal    | Exception              |

| Hardware malfunctions                         | Either      | Exception or interrupt |

| Exception type        | Exception vector address (in hex) |  |  |

|-----------------------|-----------------------------------|--|--|

| Undefined instruction | 8000 0000 <sub>hes</sub>          |  |  |

| Arithmetic overflow   | 8000 0180,,,,                     |  |  |

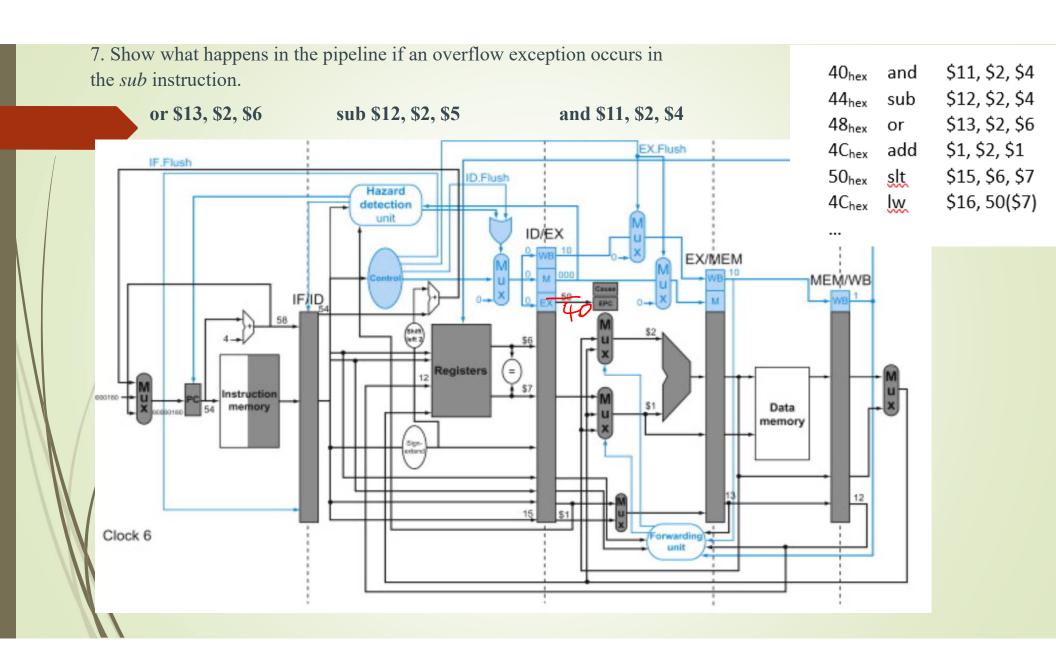

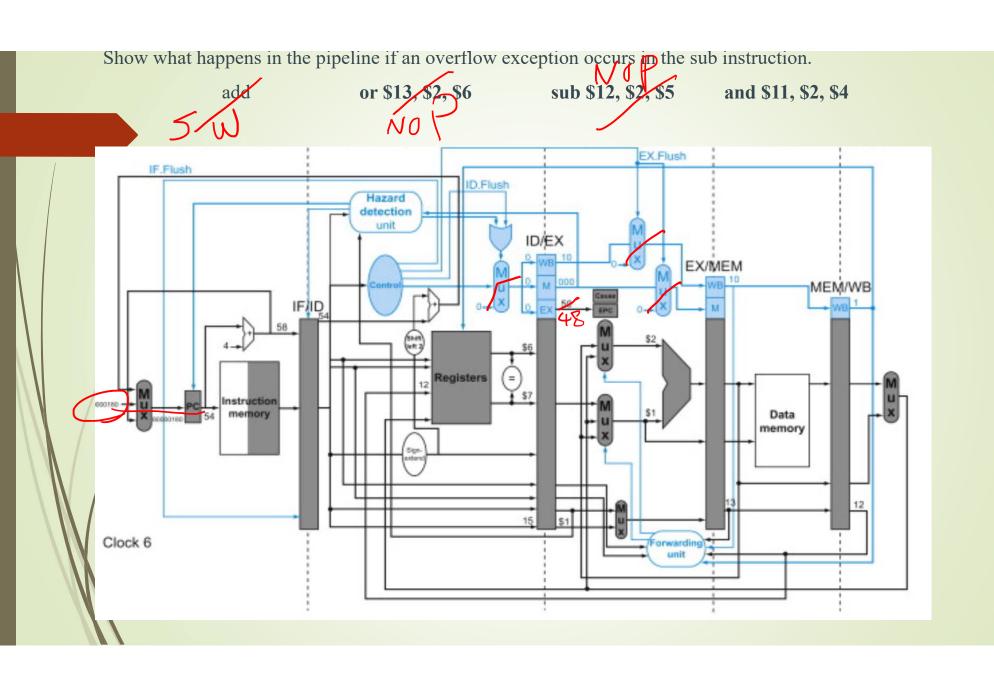

# **Exception Example**

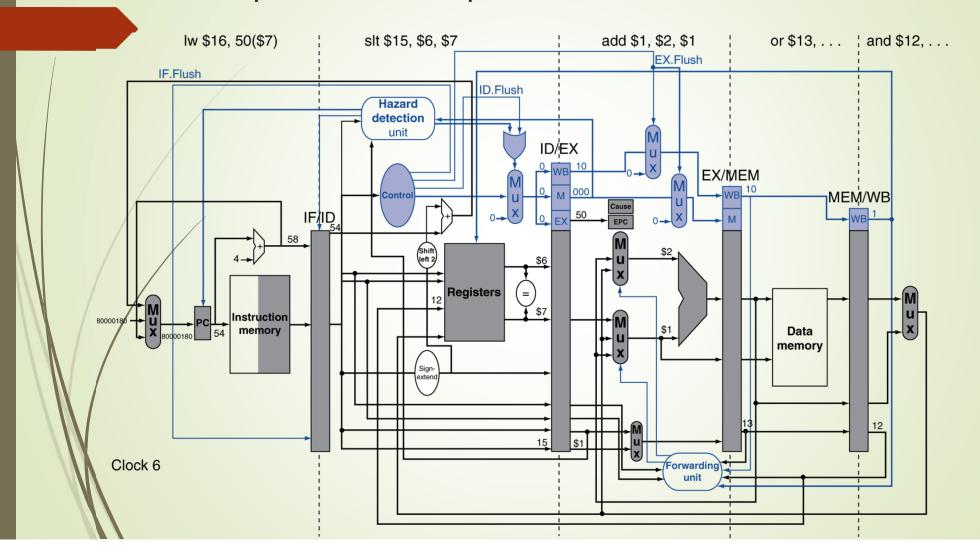

### Exception on add in

```

40 sub $11, $2, $4

44 and $12, $2, $5

48 or $13, $2, $6

4C add $1, $2, $1

50 slt $15, $6, $7

54 lw $16, 50($7)

```

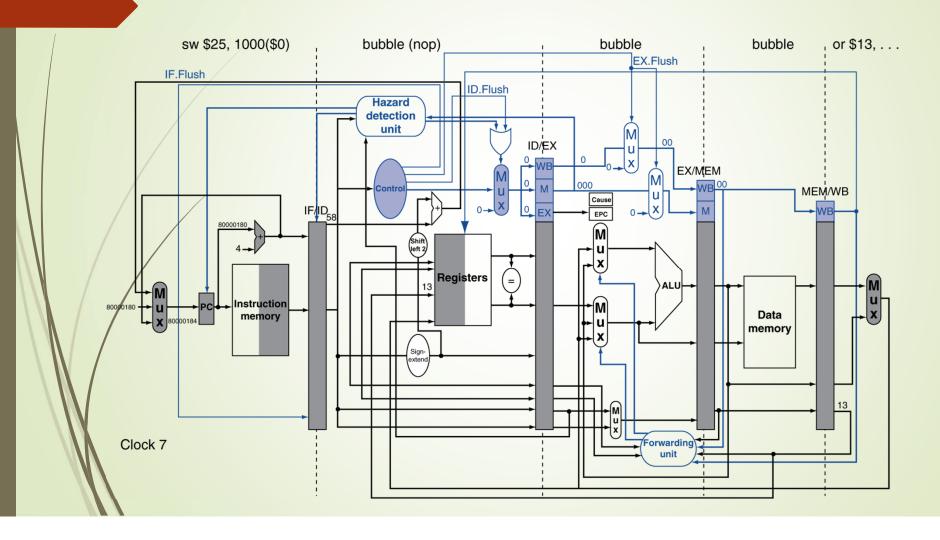

### Handler

```

80000180 sw $25, 1000($0)

80000184 sw $26, 1004($0)

```

### **Exception Example**

## **Exception Example**

| 4 | In a pipeline implementation, offending arithmetic overflow instructions are detected in the stage of the pipeline to | Correct                                                                                                         |

|---|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|   | prevent the results from being written to the stage.                                                                  | The EX.Flush signal prevents the instruction from fully executing and writing results to the WB, or write back, |

|   | O IF, ID                                                                                                              | stage.                                                                                                          |

|   | O EX, MEM                                                                                                             | -                                                                                                               |

|   | ● EX, WB                                                                                                              |                                                                                                                 |

| 9 | In the majority of MIPS implementations, multiple thrown exceptions are interrupted                                   | Correct                                                                                                         |

|   | O according to which instruction causes the largest exception                                                         | MIPS processors interrupt the earliest instruction first.                                                       |

|   | <ul> <li>according to which offending instruction is earliest</li> </ul>                                              |                                                                                                                 |

|   | O randomly                                                                                                            |                                                                                                                 |

| 6 | A(n) is always associated with an exact instruction in pipelined computers.                                           | Correct                                                                                                         |

|   | precise interrupt                                                                                                     | Designing precise interrupts is difficult and so some                                                           |

|   | O imprecise interrupt                                                                                                 | processors have imprecise interrupts.                                                                           |

| X | dd \$1, \$2, \$1 # arithmetic overflow XX \$1, \$2, \$1 # undefined instruction ub \$1, \$2, \$1 # hardware error     |                                                                                                                 |

| 4 | Which exception should be recognized first in the above sequence?                                                     | Correct                                                                                                         |

|   | arithmetic overflow                                                                                                   | The add instruction is logically executed first. The                                                            |

|   | O undefined instruction                                                                                               | overflow is detected in the EX stage and invokes the                                                            |

|   | O hardware error                                                                                                      | operating system to handle the exception.                                                                       |

|   |                                                                                                                       |                                                                                                                 |

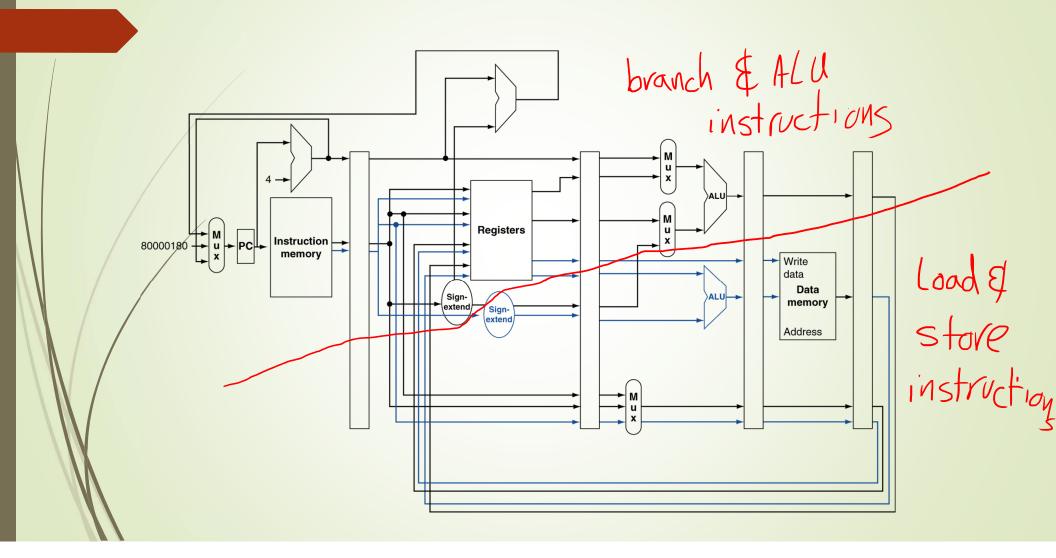

#### MIPS with Static Dual Issue

|                        | When one instruction is launched per clock cycle.                                                                                                  | Corre |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| single issue           | Single issue pipelining can achieve parallelism when instruction operations are overlapped.                                                        |       |

|                        | The parallelism between instructions.                                                                                                              |       |

| ILP                    | Pipelining exploits ILP, short for instruction-level parallelism, by launching new instructions during the latter stages of previous instructions. |       |

|                        | When multiple instructions are launched per clock cycle.                                                                                           | Corre |

| multiple issue         | Multiple issue pipelining allows the instruction execution rate to exceed the clock rate.                                                          |       |

| dynamic multiple issue | A multiple issue implementation where decisions are made during execution by the processor.                                                        | Corre |

|                        | The implementation is dynamic, because decisions are being made during runtime.                                                                    |       |

|                        | The positions available to issue instructions in a given clock cycle.                                                                              | Corre |

| issue slots            | A task of multiple issue is determining which issue slots should be used for which instructions.                                                   |       |

| static multiple issue  | A multiple issue implementation where decisions are made by the compiler before execution.                                                         | Corre |

|                        | The implementation is static because decisions cannot be changed during runtime.                                                                   |       |

### Scheduling Example

Schedule this for dual-issue MIPS

|       | ALU/branch              | Load/store        | cycle |

|-------|-------------------------|-------------------|-------|

| Loop: | nop                     | Iw (\$t0, 0(\$s1) | 1     |

|       | addi \$51, \$51, -4     | pop               | 2     |

|       | addu/\$t0, \$t0 \$s2    | nop               | 3     |

|       | bne \$\$1, \$zero, Loop | sw \$t0, 4(\$s1)  | 4     |

9. Show how the following loop can be scheduled on a static two-issue pipeline for MIPS?

```

Loop: lw $t0, 0($a1)

add $t0, $t0, $a3

sw $t0, 0($a1)

addi $a1, $a1, -12

bne $a1, $0, Loop

```

#### Computer the overall IPC.

Loop

| ALU/Branch         |                                     | Load / Store |               |

|--------------------|-------------------------------------|--------------|---------------|

| nop                |                                     | lw           | \$t0, 0(\$s1) |

| nop<br>add<br>addi | \$t0, \$t0, \$a3<br>\$a1, \$a1, -12 | SW           | \$t0, 0(\$a1) |

| bne                | \$a1, \$0, Loop                     |              |               |

• IPC =

$$5/5 = 1$$

9. Show how the following loop can be scheduled on a static two-issue pipeline for MIPS?

```

Loop: lw $t0, 0($a1)

add $t0, $t0, $a3

sw $t0, 0($a1)

addi $a1, $a1, -12

bne $a1, $0, Loop

```

Loop

Reorder the instructions to avoid as many pipeline stalls as possible. Computer the overall IPC.

• IPC =

$$5/4 = 1.25$$

### Loop Unrolling Example

```

Iw $t0, 0($s1)

addu $t0, $t0, $s2

$t0, 0($s1)

SW

addi $$1, $$1, -4

$t0, 0($s1)

I w

addu $t0, $t0, $s2

$t0, 0($s1)

SW

addi $s1, $s1, -4

$t0, 0($s1)

addu $t0, $t0, $s2

$t0, 0($s1)

addi $$1, $$1, -4

$t0, 0($s1)

I w

addu $t0, $t0, $s2

$t0, 0($s1)

addi $$1, $$1, -4

```

```

Iw $t0, 0($s1)

addu $t0, $t0, $s2

$t0, 0($s1)

SW

addi $$1, $$1, -16

l w

$t0, 12($s1)

addu $t0, $t0, $s2

$t0, 12($s1)

SW

I w

$t0, 8($s1)

addu $t0, $t0, $s2

$t0, 8($s1)

SW

l w

$t0, 4($s1)

addu $t0, $t0, $s2

$t0, 4($s1)

SW

```

```

$t0, 0($s1)

l w

addu $t0, $t0, $s2

$t0, 0($s1)

SW

addi $$1, $$1, -16

Iw $t1, 12($s1)

addu $t1, $t1, $s2

$t1, 12($s1)

SW

Iw $t2, 8($s1)

addu $t2, $t2, $s2

$t2, 8($s1)

SW

Iw $t3, 4($s1)

addu $t3, $t3, $s2

$t3, 4($s1)

SW

```

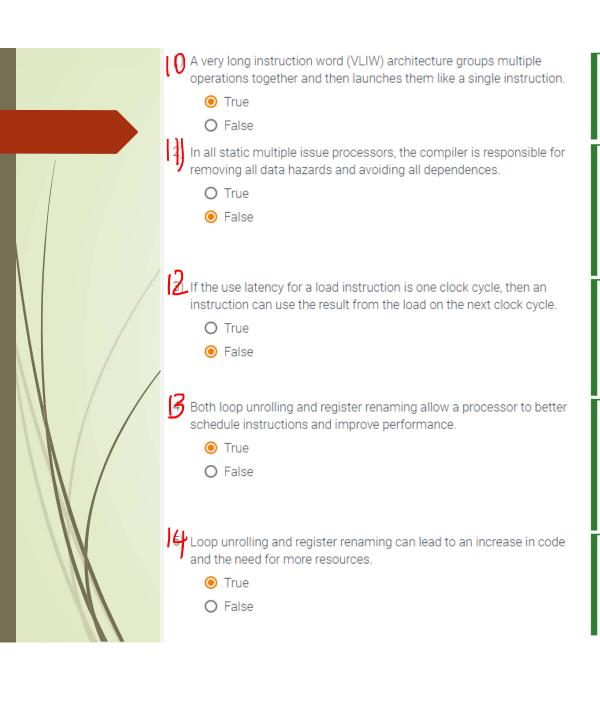

#### Correct

The term very long word instruction come from the fact that issue packets store multiple operations to be launched together like a single instruction.

#### Correct

Multiple issue processors vary in how they handle hazards and dependences. Some static multiple issue processors require the compiler to remove all data hazards. Other static multiple issue processors require the compiler to avoid all dependences within a pair of instructions.

#### Correct

A use latency of one clock cycle prevents another instruction from using the load's result on the next clock cycle without stalling. If an instruction tries to use the load's result in the next clock cycle, the new instruction will stall.

#### Correct

Loop unrolling is the act of replicating the loop body many times to issue independent instructions in parallel. Register renaming identifies independent registers and eliminates name dependences. The methods can be used separately or together to improve instruction scheduling.

#### Correct

Loop unrolling increases code by replicating the loop body a number of times. Register renaming calls for the use of temporary registers, which are additional resources. 15) Show would the following loop unrolling and register renaming can be used for 4 iteration of the following on a static two-issue pipeline for MIPS? Computer the overall IPC.

```

I w

$t0,

0(\$s1)

add

$t0, $t0, $a3

$t0,

0(\$a1)

SW

addi

$a1,

$a1,\-12

I w

add

$t0, 0($s1)

ll w

$t0,

SW

add

$t0, $t0, $a3

$a1,

addi

$t0, 0($a1)

$W

addi

$a1, $a1, -12

$t0, 0($s1)

l w

add

$t0, $t0, $a3,

$t0, 36 ($a1)

SW

0(\$s1)

add

$t\(\varphi\), $t0, $a3

$t0, 0($s1)

I w

$$0, 0($a1)

$t0, $t0, $a3

add

addi

$a1, -12

$t0, (24($a1)

SW

$t0, 0($s1)

I w

$t0, 0($s1)

I w

$t0,

add

$t0, $a3

add

$t0, $t0, $a3

$t0, 0($a1)

SW

SW

$t0, 12($a1)

addi

$a1,

$a1, -12

```

```

add $t0, $t0, $a3

sw $t0, 0($a1)

addi $a1, $a1, -12

bne $a1, $0, Loop

( $t0, 0($s1)

Id $t0, $t0, $a3

add $t0, $t0, $a3

```

Loop:

\$t0, 0(\$a1)

```

$t0,

$t0, $a3

$t0,

0(\$a1)

$a1,

$a1, -48

addi

$t1, 0($s1)

$t1, $t1, $a3

$t1, 36($a1)

$t2, 0($s1)

$t2, $t2, $a3

$t2, 24($a1)

$t3, 0($s1)

$t3, $t3, $a3

$t3, 12($a1)

```

# Loop Unrolling Example

| _            | We the second |                        |                    |       |

|--------------|-----------------------------------------------------------------------------------------------------------------|------------------------|--------------------|-------|

|              |                                                                                                                 | ALU/branch             | Load/store         | cycle |

|              | Loop:                                                                                                           | addi (\$s1) \$s1, -48  | 1w (\$t0, 0(\$s1)  | 1     |

|              |                                                                                                                 | nop                    | Iw \$t1 12(\$s1)   | 2     |

|              |                                                                                                                 | add \$t0, \$t0, \$a3   | 1w \$t2, 8(\$s1)   | 3     |

| $\mathbb{L}$ |                                                                                                                 | add \$t1, \$t1, \$a3   | Iw \$t3, 4(\$s1)   | 4     |

|              |                                                                                                                 | add \$t2, \$t2, \$a3   | sw (\$t0, 48(\$s1) | 5     |

|              |                                                                                                                 | add \$t3, \$t3, \$a3   | sw \$t1, 36(\$s1)  | 6     |

| 1            | /                                                                                                               | nop                    | sw \$t2, 24(\$s1)  | 7     |

| 1            |                                                                                                                 | bre \$a1, \$zero, Loop | sw \$t3, 12(\$s1)  | 8     |

Closer to 2, but at cost of registers and code size

```

Iw $t0, 0($s1)

add $t0, $t0, $a3

sw $t0, 0($a1)

addi $a1, $a1, -48

Iw $t1, 0($s1)

add $t1, $t1, $a3

$t1, 36($a1)

SW

$t2, 0($s1)

l w

add $t2, $t2, $a3

$t2, 24($a1)

SW

$t3, 0($s1)

l w

add $t3, $t3, $a3

$t3, 12($a1)

SW

```